Transistores en rascacielos: la revolución que comprime circuitos como ciudades verticales

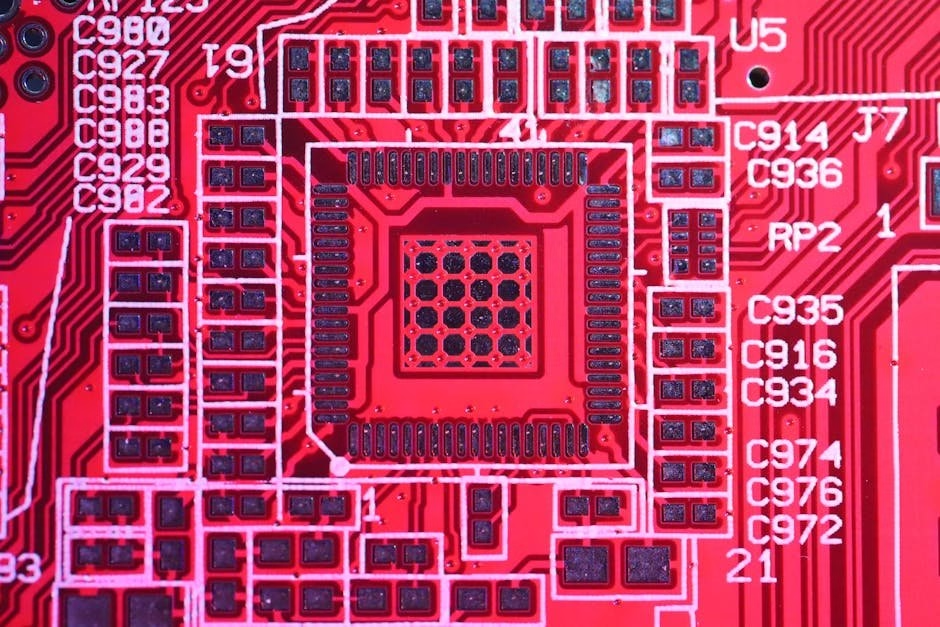

Imagina una ciudad donde el espacio es tan valioso que los edificios no crecen hacia los lados, sino hacia el cielo. Rascacielos que albergan miles de hogares y oficinas en una fracción del terreno que requerirían si estuvieran extendidos horizontalmente. Esta misma lógica urbana está llegando ahora al corazón de la tecnología moderna: los circuitos integrados. En un avance que podría redefinir el futuro de la electrónica, investigadores de TSMC han demostrado que es posible apilar transistores verticalmente, creando lo que podríamos llamar “rascacielos de silicio”.

El desafío del espacio en la era de la miniaturización

Desde la invención del transistor en 1947, la industria electrónica ha perseguido una meta constante: empaquetar más componentes en menos espacio. La Ley de Moore, que predijo que el número de transistores en un chip se duplicaría aproximadamente cada dos años, ha guiado esta carrera durante décadas. Sin embargo, como cualquier tendencia exponencial, eventualmente encuentra barreras físicas.

Los materiales convencionales utilizados en la fabricación de transistores están alcanzando sus límites fundamentales. Cuando los componentes se vuelven demasiado pequeños, fenómenos cuánticos como el efecto túnel comienzan a interferir con su funcionamiento normal. Además, la disipación de calor se convierte en un problema crítico cuando millones de transistores están empaquetados en un área minúscula.

La solución vertical: cuando el plano no es suficiente

En su presentación en la Reunión Internacional de Dispositivos Electrónicos de IEEE 2025, el equipo de Liao de TSMC propuso una solución radicalmente diferente. En lugar de seguir comprimiendo transistores en un plano bidimensional, ¿por qué no construir en tres dimensiones?

La investigación describe dos circuitos lógicos donde se apilan dos tipos diferentes de transistores uno sobre otro, similar a cómo los pisos de un edificio albergan diferentes tipos de espacios (residenciales, comerciales, de servicios). Este enfoque no es simplemente una disposición diferente de componentes existentes, sino que requiere innovaciones significativas en:

- Materiales semiconductores avanzados

- Técnicas de fabricación a nanoescala

- Diseño arquitectónico de dispositivos

- Gestión térmica en estructuras 3D

Implicaciones tecnológicas y sociales

La capacidad de construir circuitos en tres dimensiones podría tener consecuencias profundas para múltiples sectores tecnológicos. Los dispositivos celulares podrían volverse aún más potentes sin aumentar su tamaño físico. Los centros de datos podrían reducir drásticamente su huella espacial y energética. La inteligencia artificial, que requiere cantidades masivas de procesamiento paralelo, encontraría en esta tecnología un aliado natural.

Un paralelismo histórico fascinante

Curiosamente, esta evolución tecnológica refleja patrones que hemos visto antes en la historia humana. Así como las ciudades medievales crecían dentro de murallas defensivas, forzando la construcción vertical, la electrónica enfrenta ahora sus propias “murallas” físicas. La solución, en ambos casos, ha sido pensar en la tercera dimensión.

Este paralelismo nos recuerda que la innovación tecnológica a menudo sigue patrones que ya existen en otros dominios del conocimiento humano. La biomimética (inspirarse en la naturaleza) tiene ahora un equivalente en lo que podríamos llamar “socio-mimética”: inspirarse en las soluciones que las sociedades humanas han desarrollado para problemas similares.

El futuro de la computación tridimensional

El trabajo de TSMC representa solo el comienzo de lo que podría convertirse en una nueva era de la electrónica. Los circuitos integrados tridimensionales podrían permitir:

- Mayor densidad de componentes sin reducir el tamaño de los transistores individuales

- Mejor eficiencia energética al reducir las distancias que deben recorrer las señales eléctricas

- Arquitecturas de procesamiento más especializadas y eficientes

- Integración de diferentes tipos de tecnología en un mismo paquete

Sin embargo, como con cualquier tecnología emergente, existen desafíos significativos. La fabricación de estructuras 3D complejas requiere precisión a nivel atómico. La disipación de calor en estructuras apiladas es más complicada que en diseños planos. Y los costos de desarrollo e implementación inicial serán considerables.

La equidad en el acceso a la tecnología

Un aspecto crucial que a menudo se pasa por alto en discusiones sobre avances tecnológicos es cómo asegurar que sus beneficios se distribuyan equitativamente. La tecnología de transistores apilados podría, en teoría, hacer que la computación de alto rendimiento sea más accesible al reducir costos a largo plazo. Sin embargo, también podría concentrar aún más la capacidad de fabricación avanzada en unas pocas empresas con los recursos para desarrollar estas tecnologías.

Este dilema nos recuerda la importancia de considerar no solo el “cómo” técnico de las innovaciones, sino también el “para quién” y el “con qué consecuencias sociales”. La historia de la tecnología está llena de ejemplos de avances que, aunque técnicamente impresionantes, exacerbaban desigualdades existentes.

Conclusión: más allá de la Ley de Moore

La investigación de TSMC sugiere que, aunque podamos estar acercándonos a los límites de la miniaturización horizontal, el espacio vertical ofrece nuevas fronteras por explorar. Así como las ciudades descubrieron que podían crecer hacia el cielo cuando el terreno escaseaba, la electrónica está aprendiendo la misma lección.

Este avance no es solo una curiosidad técnica, sino un recordatorio de que la innovación a menudo viene de cambiar nuestra perspectiva fundamental sobre un problema. Cuando algo parece imposible en una dimensión, la solución puede estar literalmente en otra dimensión.

La próxima vez que veas un rascacielos, piensa que dentro de tu teléfono o computadora podría estar ocurriendo una miniaturización similar. La arquitectura urbana y la arquitectura de chips están convergiendo en principios fundamentales sobre cómo optimizar el espacio cuando este se vuelve nuestro recurso más preciado.